2023年9月14日の日記の1番目の記事へのコメント

■基板

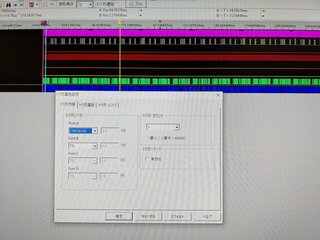

CPS1の信号回りを見ていて、ふと気になってロジアナの設定を確認したところ、トリガレベルがTTLになっていました。もしかして、これ、CMOSレベルで見ないとだめだった・・・?とりあえず、PICが何もしていないとき、普段はHIGHになっていたデータバスが、スレッショルドが変わったことでLOW表示になりましたw

で、今日は、CPS-A-01によるメモリアクセスを避ける上で、OBJEOに代わってHSYNC同期できないか実験してみました。OBJEOだとトグルする回数が少ない関係で、これに同期しちゃうとどうしてもCPUリセット解除までにできることが限られてしまうんで。HSYNCなら60μ秒程度の周期でずっと出続けているはずです。

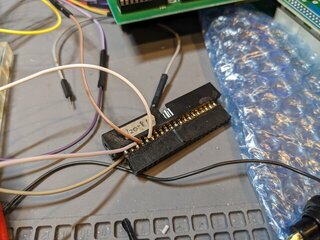

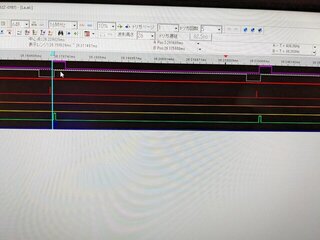

Cボードの116番ピンから信号を引き出して観測してみると、HSYNCはOBJEOと同じくらいの時間LOWになっていることが判明 (波形のグレーがHSYNC、紫がOBJEO)。CPS-A-01によるデータバスへのアクセスタイミング (波形の緑と青) とほぼ同時にHIGHに戻ってる感じですが、ここを狙って同期すれば、PICの遅さも相まって、ちょうどいい感じに処理を挟めそうです。

HSYNCに同期してキーを書くようにし、さらにメモリアクセス競合を避けるようにプログラムを修正してみたところ、チキチキボーイズでも起動してくれました。ただ、不安定で、ダメなときも多めです。

波形を観察してみると、今まで見てきた通り電源投入直後からデータが流れまくるパターンと、逆に一切データが流れないパターンの2種類があることがわかりました。後者のようなケースになる場合があったとは気が付かなかった・・・。そして、後者のパターンに当たるとうまく起動して、逆に前者のパターンに当たると起動しない傾向にあるようです。うむむ、これはもしや・・・。

2023年9月14日の日記の1番目の記事へのコメント

[コメントを書く]