2023年12月10日の日記の1番目の記事へのコメント

■基板

今日もCPS1のBボードやPALについて調べたり。90629B系は、16bit幅の4Mbit ROM用のソケットが超たくさんあるけど、27番までのグラフィックデータ用のソケットは右半分と左半分で排他なんですね。右側が普通のUVEPROM (27C4096系) のピンアサインで、左側が Mask ROM用のピンアサインになってる感じ。後者に UVEPROMを取り付けようと思うと 27C4100や27C400なんかが必要になるわけですね。

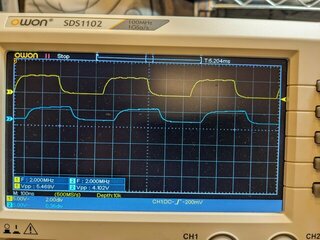

また、PALの入力信号を見てみると、1番ピンのクロックとは別に、17番ピンにも位相が少しずれたクロックが来ているようです。91634B系のBボードのPALにも11番ピンに同じような信号が来ていたりするんですが、タイミング調整用ですかね。89624B系より前のBボードにはないようです。

91634Bを使っている1941の再販版のPALをダンプしたもの (なぜか普通にダンプできる) をjedutil見てみると 、クロックとクロックを遅延させた信号の XORがROMのOE_として出ています (つまり両方がHighときか両方がLowのときだけOE_がLowになってROMからデータが出力されるようになる)。やはり信号タイミングを調整するための何かかな。

/o19 = /i1 & /i11 +

i1 & i11

o19.oe = vcc

2023年12月10日の日記の1番目の記事へのコメント

[コメントを書く]