2023年9月6日の日記の1番目の記事へのコメント

■基板

CPUがリセットを解除する前にデータバスに信号を出しているのは誰なのか、VARTHのM/Bを使って調べてみました。

とりあえずM/B単体だと、リセット解除までの間にデータバスに信号が出ることはなさそうです。

続いてプログラムROMがほとんど載っていないマジックソードのサブボードを載せてみましたが、こちらも無風。なるほど・・・

VARTHのサブボードに交換してみたら、データバスに信号が出てきました。

うーん、プログラムROMが怪しそうですね。そこで、試しにVARTHのプログラムROMの先頭の方のやつを抜いてやったらデータバスに信号が出なくなりました。

つまり、だれかがCPU起動前にROMを読みに行っていて、そのデータがデータバス上で見えてしまっているようです。プログラムROMからデータが出ているということは、プログラムROMのOEを操作しているのが誰かを追えば、読み出し主がわかるかもしれません。

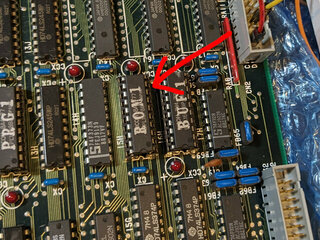

ROMのOEはどこから来ているのかを追ってみたところ、ROM1というPALから来ていました。このPAL自体はM/B間で共通のはずです。だとすると、PALのロジック自体が原因ではなく、そこに入力されている信号に違いがあって、VARTHのM/BではOEが動いてしまっているものと推測されます。

PALの入力と思われる線を追ってみると、CPS-A-01の方から来ているものがあるようです。うーん、なるほど、Aチップか。しかし、M/Bによって差があるというのはどういう違いなのか。まさかCPS-A-01のロットによって違ったりするんですかね・・・。

2023年9月6日の日記の1番目の記事へのコメント

[コメントを書く]