2023年9月10日から2023年9月6日までの日記を表示中

2023年 9月10日 (日)

■基板

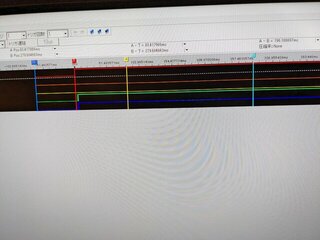

昨日、CPS-B-21のピン上げ改造を試した結果、やはり起動時キー書き込みの実施において、61番ピンと62番ピンのピン上げは回避したいという思いが強まりました。しかし、そのためにはCPUリセット解除前にデータバス側に出てくる信号を抑制しなければなりません。というわけで、CPS-A-01がどういう経緯でメモリアクセスを引き起こすのかについてちょっと調べてみました。

ひとまずCPS-A-01の解析ドキュメントにヒントがないか探してみたところ、こちらのドキュメントにCPS-A-01によるバスアクセスに関する記述がありました。 ドキュメントによると、CPS1では、CPU以外でバスを利用するデバイスはCPS-A-01だけらしく、また、普通に68000のバスプロトコル (使いたい人が要求 (Bus Request (BR)) を出した後、CPUが許可 (Bus Grant (BG)) を出して、使う人が使っている間 Bus Grant Ack (BGACK) を上げておく) に従っているようです。

ただ、CPS-A-01のピンアサインを見るとBRとBGACKはあるのにBGがありません。しかもBGACKは出力ではなく入力のようです。つまり、CPS-A-01がBRを出してCPUがBGを出したら、CPS-A-01以外の誰かがBGACKを出して、それをCPUとCPS-A-01の双方が受け取るようになっているということなんですかね。

この辺の信号がどう作られているのかを調べて、キー書き込み中にBGACKが出ないように何らかの方法で抑え込んでやれば、CPS-A-01がバスにデータを流すこともなくなるのでは・・・と思って回路を追ったりロジアナで観察したりしてみたんですが、どうも68000はRESETやHALTが有効になっている間も普通にBGを出す一方、BGACKも周辺の汎用ロジックで組まれた回路によってBGが出た一定サイクル後に勝手に出るような作りになっているように見えます。というわけでこの作戦はボツに。残念。

他に手はないかと、改めて先程の解析ドキュメントを見てみたところ、「CPS-A-01は特定の動作状態に入った場合に外部メモリにアクセスをする」といったことが書かれていました。そしてIDLE状態にいる限りは外にアクセスをしないようです。ということは、CPUが起動するよりも前に、何らかの理由で勝手にIDLE以外の状態に遷移してしまうということなのかな?この状態遷移の要因を排除できれば安全にキー書き込みができるかもしれません。次はこれか・・・。

2023年 9月 9日 (土)

■基板

これまでCPS1での起動時キー書き込みは、BボードとCボードの間にアダプタを入れて、そこで一部の信号をバイパスする形で行ってきましたが、これだとどうしても基板の高さが増してしまうため、例のカプコンワールド2やVARTHのケースに収まらないという問題が生じます。

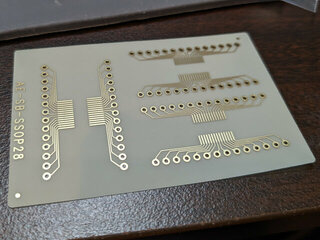

で、ちょっと前にこの問題を回避するナイスな方法を閃いたので、今日はそれを試してみることにしました。使うのは秋月電子で売っている超薄型の0.65mmピッチ SSOP28用ピッチ変換基板です。 正直、思いついた時点では基板を起こす覚悟だったんですが、まさかこんなドンピシャなものが市販されていようとはw

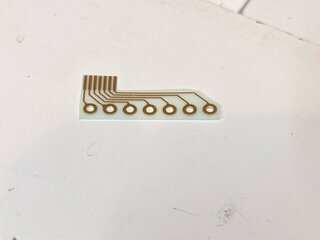

これをこんな風に7ピン分を切り出します。カッターよりもハサミで切った方が楽ですね。

もう一つ、こんな感じで2ピン分を切り出します。

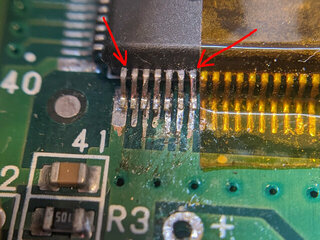

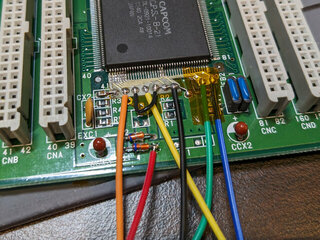

次にCボード (今回は 92641C-1) のCPS-B-21のピンを上げていきます。まずは41番ピンから47番ピンまで。

そして同様に61番ピンと62番ピンも上げます。

41番ピンの近くにカプトンテープを貼り、絶縁処理 (この後もうちょっと貼り足しました)。

そしたら、最初に切り出したピッチ変換基板を上げたピンの下に差し込みます。

そして先程持ち上げた7本のピンをハンダ付けします。

41番ピン、43番ピン、45〜47番ピンはGNDに配線すべき信号なので、繋ぎつつ、ちょうど変換基板の左右にあったGNDのパターンに適当な端材でCボードに固定w

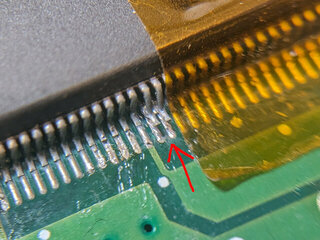

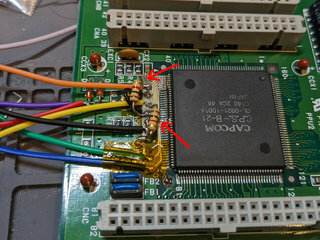

もう一つの切り出したピッチ変化基板も、同様に61番ピンと62番ピンの下に滑り込ませて、持ち上げたピンをハンダ付けします (写真はその後、上からカプトンテープを貼った状態なのでわかりにくいですが・・・)

後は42番ピン、44番ピン、61番ピンおよび62番ピンの信号を個別に引き出します。ついでに+5V とGNDも引き出し。61番ピン・62番ピンの下に入れたピッチ変換基板は、うまくCボードに固定できていないため、ひとまずカプトンテープを上から貼って補強しています。非常に見苦しい・・・w

早速VARTHで試してみます。マルチプレクサに入れるBボード側の信号は、Cボードのコネクタ部分から取得しています。

起動しました!やった!

が、しばらく放置していたところ、いつの間にか画面がブラックアウト。何やら不安定なようです・・・って、42番ピンと44番ピンをCボードから外した後、プルダウンするのを忘れていました (元々はR1とR2でプルダウンされている)。というわけで、雑にプルダウン抵抗を追加w

これで安定したっぽいです。いやー、イメージしていた方法が実際に可能であることが実証できて良かったです。ただ、実装難易度は置いておくにしても、61番ピン・62番ピンの下に割り込ませたピッチ変換基板が固定できていないなど、課題も多いですね。というか、M/B側から変な信号が来なければ、そもそも61番ピンと62番ピンには細工が不要なんですよね。うーん、何とかできないかなぁ。

[コメントを書く]

2023年 9月 8日 (金)

■コネクタ

CPicS1で使えるであろう 40ピンのキー付きのメスコネクタ (ワイドタイプ) が届きました。AliExpressのショップに在庫がなくて、いつ頃入荷するか問い合わせたら、わざわざ仕入れてくれた模様。ありがたい。量産することになったらたくさん買いますw

[コメントを書く]

■基板

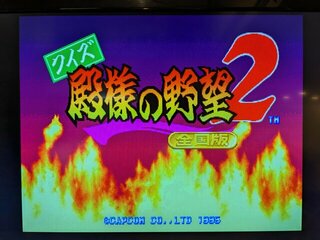

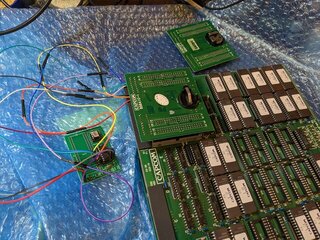

昨日の続き。起動時にCPS-B-21にキーを書き込む間だけ、CPS-B-21のデータバスの下位2bitをサブボード側から切り離しておく実験です。CPicSKと同じ74HC4053 (マルチプレクサ・デマルチプレクサ) を使うことで簡単に実現できそうだったので、CPicSKの試作基板の余りを使って作ってみましたw

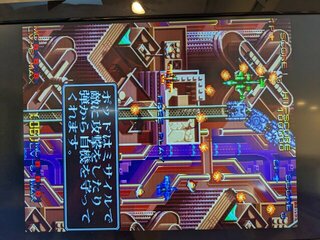

おお、動いた。殿様の野望2が動きました。大成功です。

チキチキボーイズもVARTHも、それぞれのマザーボードで試してみましたが、いずれも問題なく起動時キー書き込みに成功しました。

とにかく非常に安定していますね。素晴らしい。

[コメントを書く]

2023年 9月 7日 (木)

■ティアーズオブザキングダム

[コメントを書く]

■基板

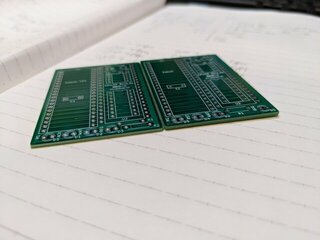

CPicSKのRev1.0cの基板が届きました。92636D-3にも対応するよう、抵抗のパターンを追加したバージョンです。

今回は基板の厚さを1.6mmから1.2mmに減らしています。これでピンヘッダのハンダ付けも、多少はやりやすくなるかな?

[コメントを書く]

■基板

昨日の調査で、CPS1のM/BにおいてCPUリセット解除前にデータバスにデータを流しているのはCPS-A-01っぽいということはわかったんですが、そういうM/Bでも起動時のキー書き込みを安全に行えるようにするには、キー書き込み中、CPS-B-21のデータバスの下位2bitをBボードから切り離した状態としておく必要がありそうです。

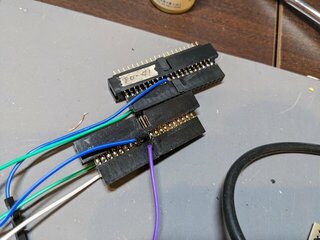

というわけで、これを試すために、新たにデータバスに割り込むためのコネクタを作成しました (写真下側)。単にBボード - Cボード間で61番ピンと62番ピンを繋がないようにして、Bボード側とCボード側の両方から配線を引き出しています。

これを使って、CPS-B-21に対して、Bボード側の信号とPICの信号のどちらを繋ぐか、マルチプレクサで切り替えるようにする作戦。

[コメントを書く]

2023年 9月 6日 (水)

■基板

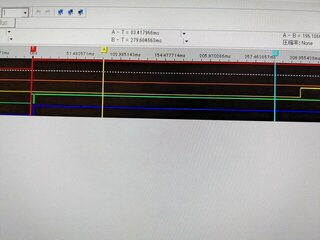

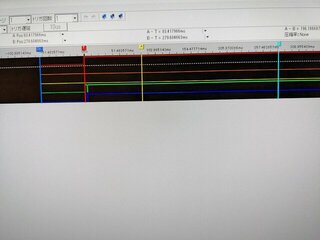

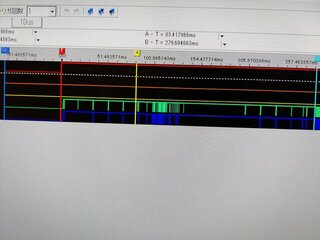

CPUがリセットを解除する前にデータバスに信号を出しているのは誰なのか、VARTHのM/Bを使って調べてみました。

とりあえずM/B単体だと、リセット解除までの間にデータバスに信号が出ることはなさそうです。

続いてプログラムROMがほとんど載っていないマジックソードのサブボードを載せてみましたが、こちらも無風。なるほど・・・

VARTHのサブボードに交換してみたら、データバスに信号が出てきました。

うーん、プログラムROMが怪しそうですね。そこで、試しにVARTHのプログラムROMの先頭の方のやつを抜いてやったらデータバスに信号が出なくなりました。

つまり、だれかがCPU起動前にROMを読みに行っていて、そのデータがデータバス上で見えてしまっているようです。プログラムROMからデータが出ているということは、プログラムROMのOEを操作しているのが誰かを追えば、読み出し主がわかるかもしれません。

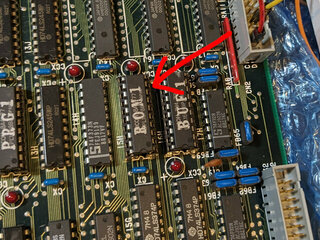

ROMのOEはどこから来ているのかを追ってみたところ、ROM1というPALから来ていました。このPAL自体はM/B間で共通のはずです。だとすると、PALのロジック自体が原因ではなく、そこに入力されている信号に違いがあって、VARTHのM/BではOEが動いてしまっているものと推測されます。

PALの入力と思われる線を追ってみると、CPS-A-01の方から来ているものがあるようです。うーん、なるほど、Aチップか。しかし、M/Bによって差があるというのはどういう違いなのか。まさかCPS-A-01のロットによって違ったりするんですかね・・・。

[コメントを書く]

■SSD

安くなっていたのでSATAのSSD (EXCERIA 960GB) を買いましたw。デスクトップ機に細々とした容量のやつが載っているので、これを統合しつつ、空いた小さいやつは古いデスクトップにつけてLinuxを入れて・・・とかやりたいけど結局増設して終わりになりそうw

[コメントを書く]

2023年9月10日から2023年9月6日までの日記を表示中

[コメントを書く]